## United States Patent [19]

DiGiulio et al.

[11] Patent Number:

4,701,856

[45] Date of Patent:

Oct. 20, 1987

| [54] | RESET DELAY CIRCUIT FOR AN |

|------|----------------------------|

|      | ELECTRONIC POSTAGE METER   |

[75] Inventors: Peter C. DiGiulio, Easton, Conn.;

Warren G. Hafner, Lake Carmel, N.Y.; Henry Stalzer, Danbury,

Conn.

[73] Assignee: Pitney Bowes Inc., Stamford, Conn.

[21] Appl. No.: 710,874

[22] Filed: Mar. 12, 1985

[58] Field of Search ...... 564/464, 466, 200, 900

[56]

## References Cited

## U.S. PATENT DOCUMENTS

| 3,978,457 | 8/1976  | Check, Jr. et al | 364/200 |

|-----------|---------|------------------|---------|

| 4,547,853 | 10/1985 | Eckert           | 364/464 |

| 4,578,774 | 3/1986  | Muller           | 364/466 |

Primary Examiner—Felix D. Gruber Assistant Examiner—Danielle Laibowitz

Attorney, Agent, or Firm—Michael J. DeSha; Melvin J. Scolnick; David E. Pitchenik

## [57] ABSTRACT

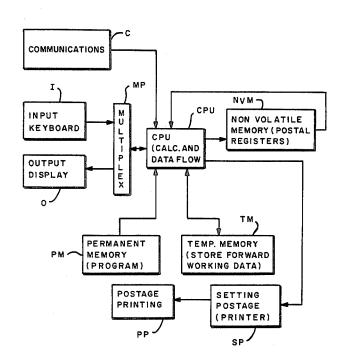

An electronic postage meter with a circuit to provide for a delay period before operation of a postage meter is disclosed. The circuit provides a fixed delay which is triggered when three input signals provided to the circuit become active. The input signals will be active in this embodiment to indicate satisfactory regulated voltage level, a satisfactory unregulated voltage level, and a satisfactory external clock frequency respectively. The output of the delay circuit upon acceptance of these active signals provides a reset delay signal to a system processor and also controls the signals that are provided to the non-volatile memories and the system printer. The circuit uses advantageously logic devices to provide the delay of the output signal rather than the traditional utilization of R-C network. The delay circuit is particularly useful in a system such as postage meter that utilizes a microprocessor and a non-volatile memory, to protect the contents of the non-volatile memory.

5 Claims, 11 Drawing Figures